First Edition: 2009

# Microprocessors and Interfacing

A. P. Godse D. A. Godse

Technical Publications Pune®

# Strictly According to the Revised Syllabus of JNTU - 2005 Course

# Microprocessors & Interfacing

[EC 05400] Third Year, B. Tech., Semester-II (ECE / Elex. & Comm. / Elex. & Telematics / I.T. / Bio. Medical)

Third Year, B. Tech., Semester - I (Instru. & Control)

#### Atul P. Godse

M. S. Software Systems (BITS Pilani)

B.E. Industrial Electronics

Formerly Lecturer in Department of Electronics Engg.

Vishwakarma Institute of Technology

Pune

#### Mrs. Deepali A. Godse

B.E. Industrial Electronics, M. E. (Computer)

Assistant Professor in Bharati Vidyapeeth's

Women's College of Engineering

Pune

Price Rs. 285/-

Visit us at: www.vtubooks.com

Technical Publications Pune

This one

(1)

# Syllabus

### (Microprocessors & Interfacing)

#### Unit-I (Chapter-1, 2)

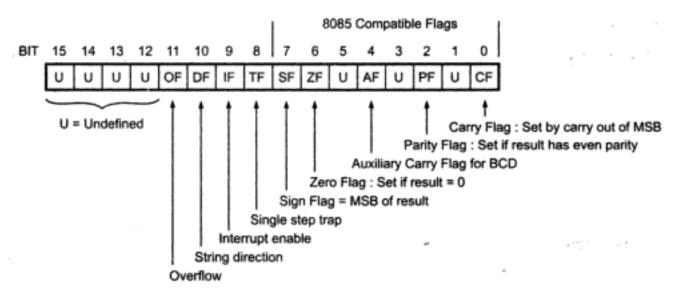

An overview of 8085, Architecture of 8086, Microprocessor, Special functions of general purpose registers, 8086 flag register and function of 8086 flags.

#### UNIT-II (Chapter-3)

Addressing modes of 8086, Instruction set of 8086, Assembler directives simple programs, Procedures, and Macros.

#### UNIT-III (Chapter-4)

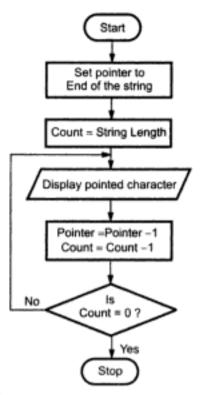

Assembly language programs involving logical, Branch and Call instructions, Sorting, Evaluation of arithmetic expressions, String manipulation.

#### UNIT-IV (Chapter-5, 6)

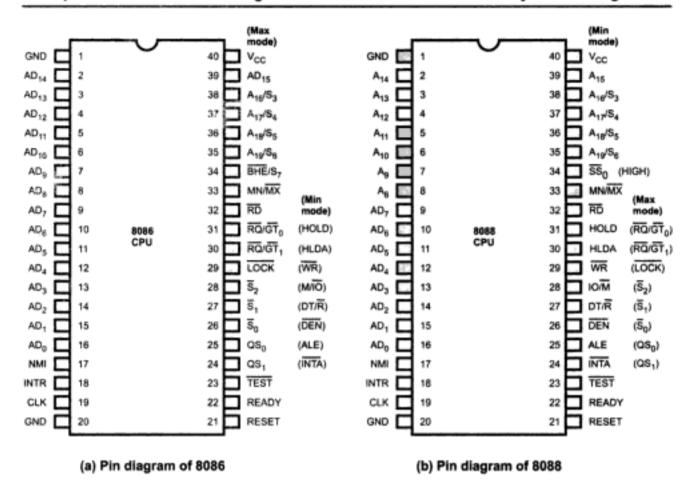

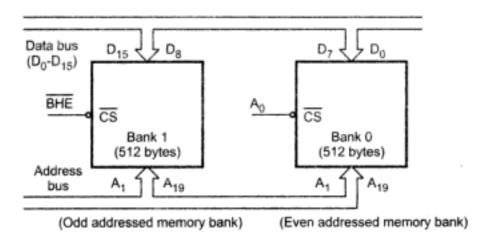

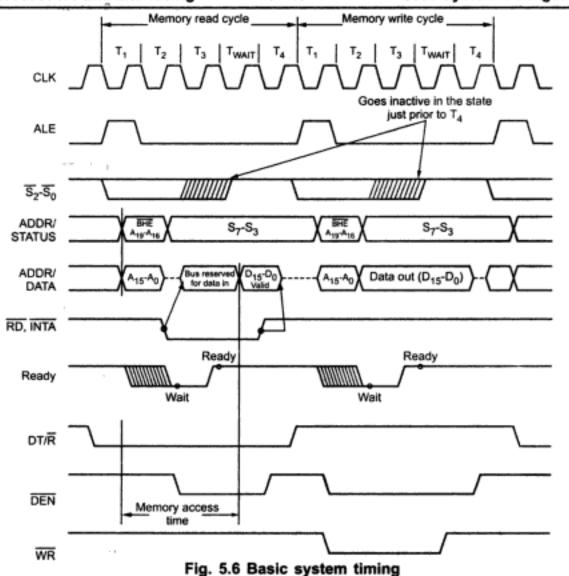

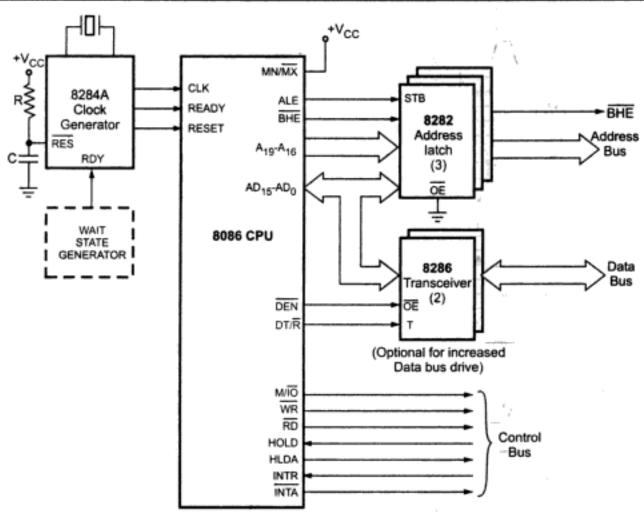

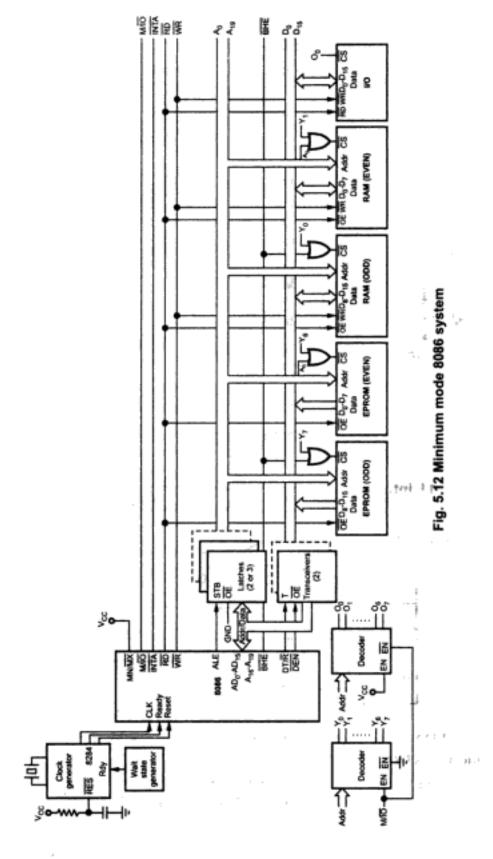

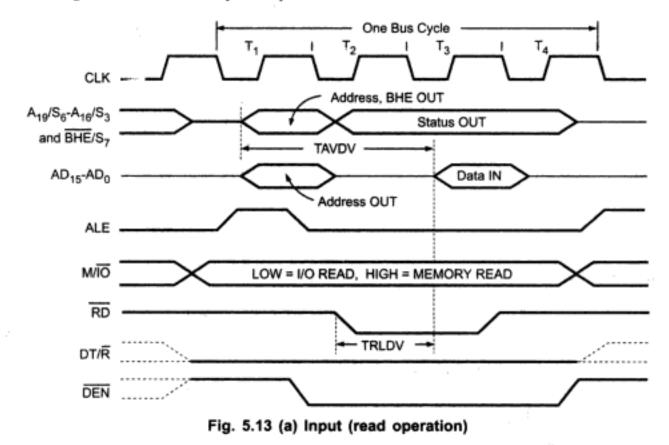

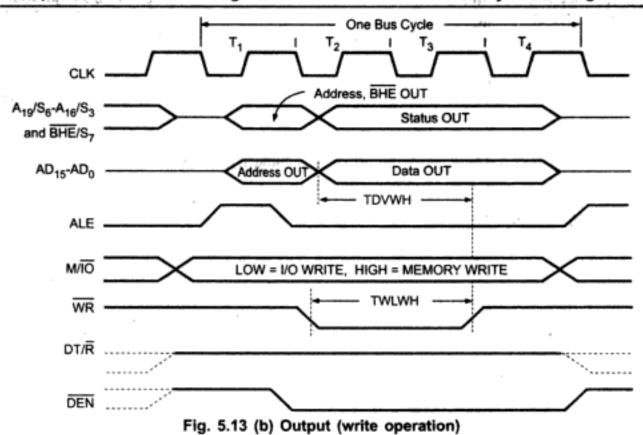

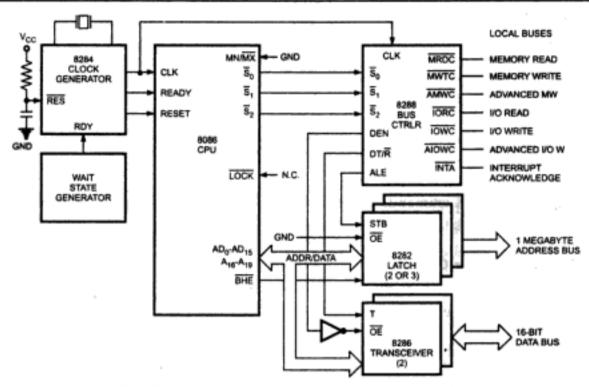

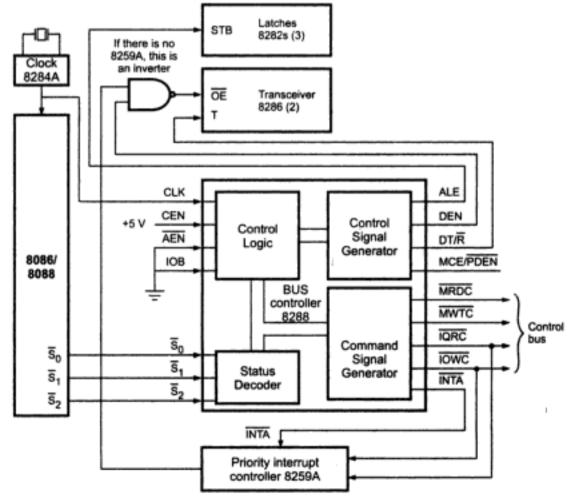

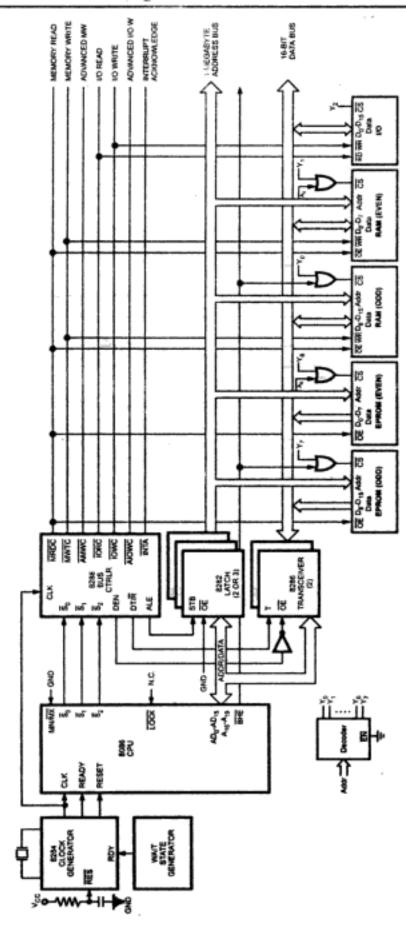

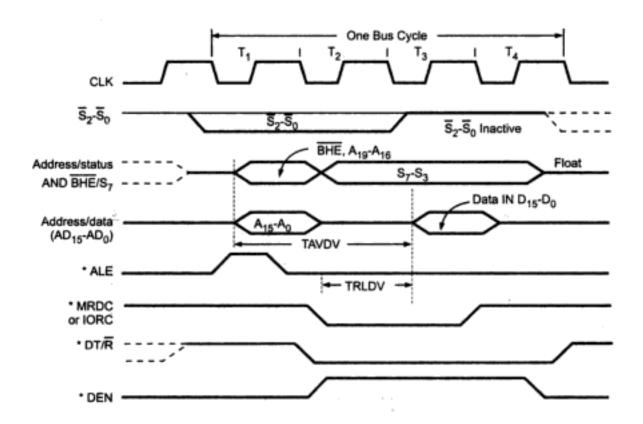

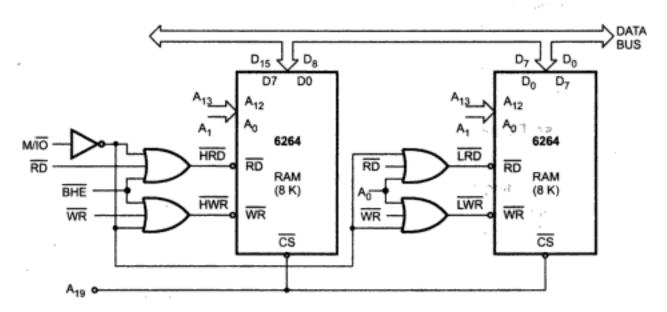

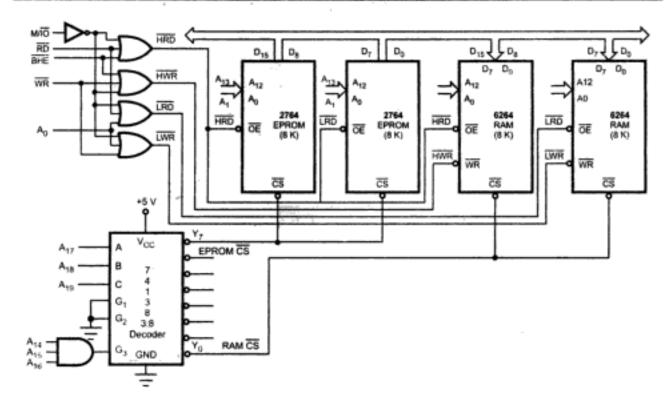

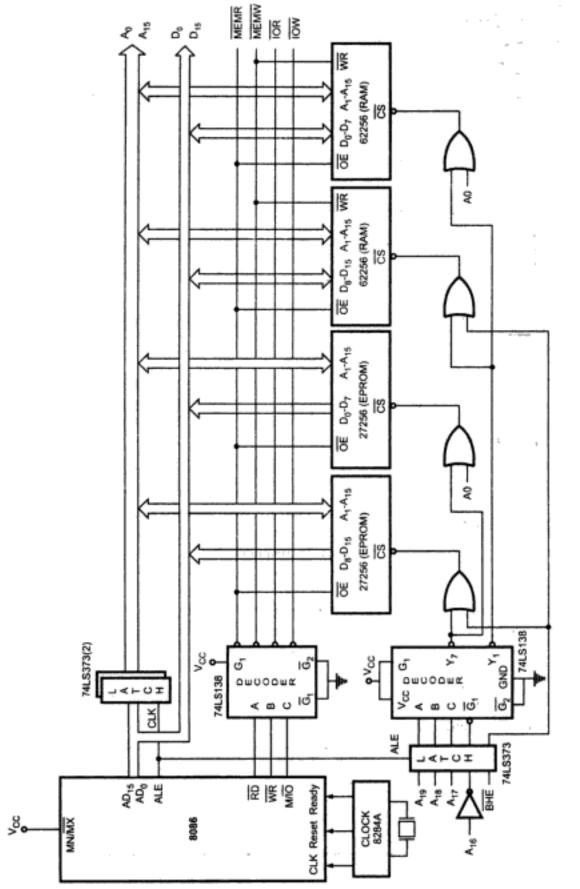

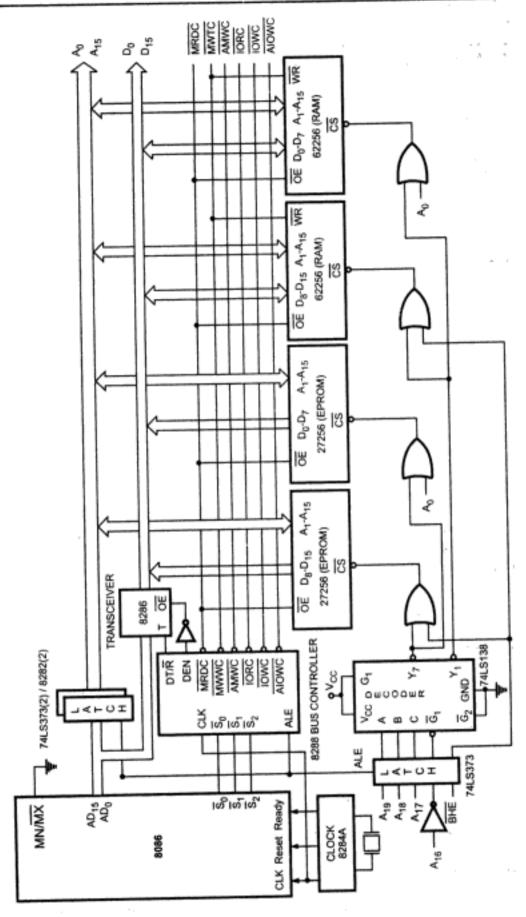

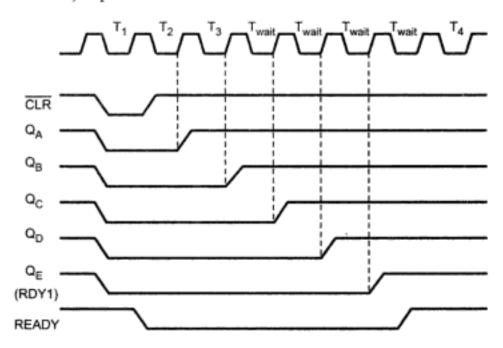

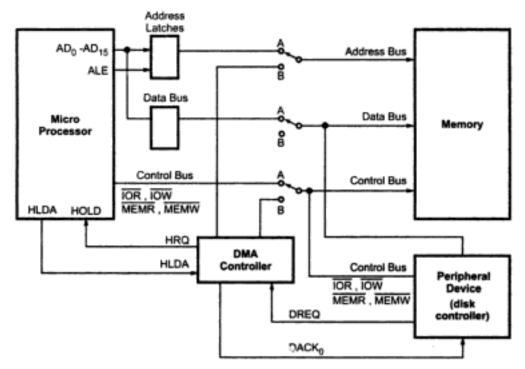

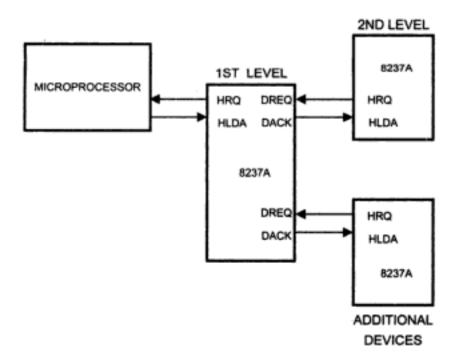

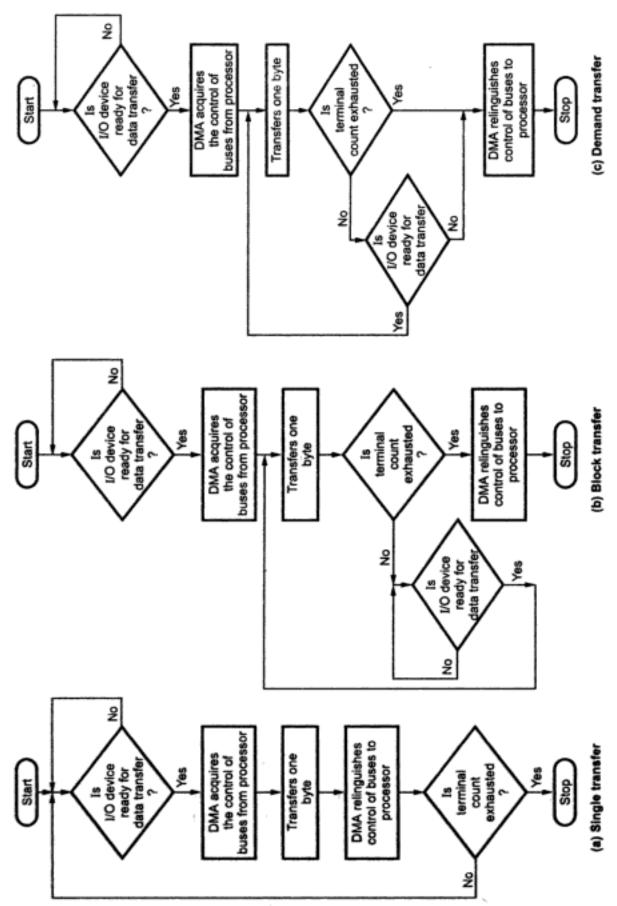

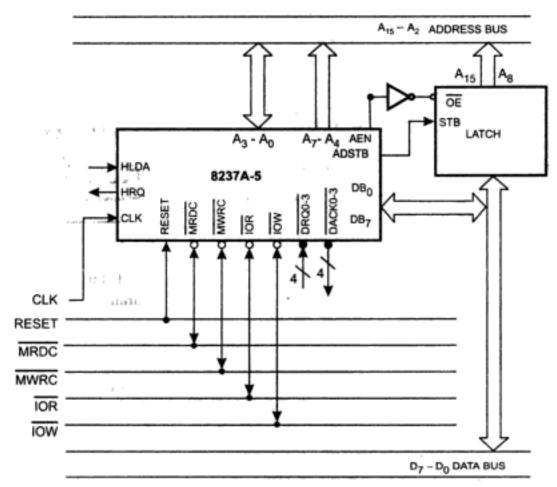

Pin diagram of 8086-Minimum mode and maximum mode of operation, Timing diagram, Memory interfacing to 8086 (Static RAM and EPROM), Need for DMA, DMA data transfer method, Interfacing with 8237/8257.

#### UNIT-V (Chapter-7)

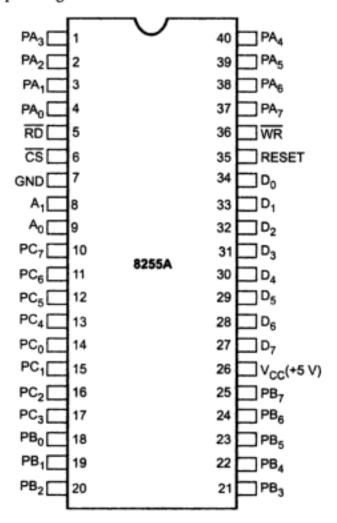

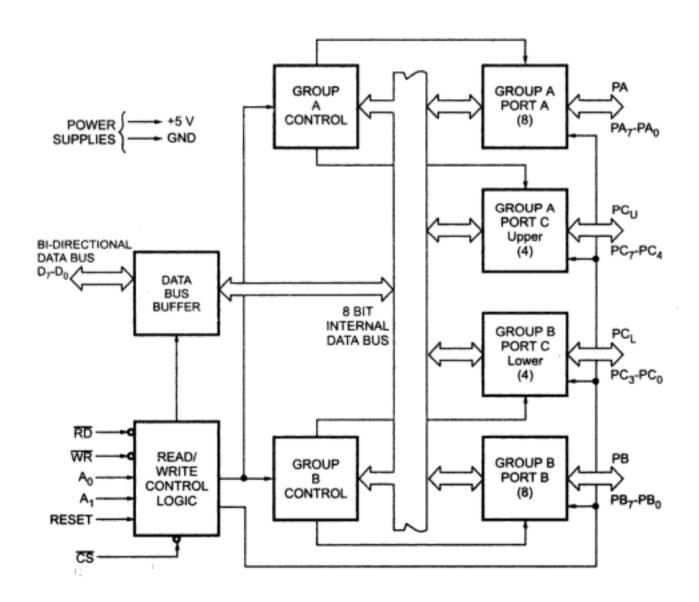

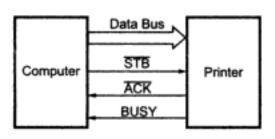

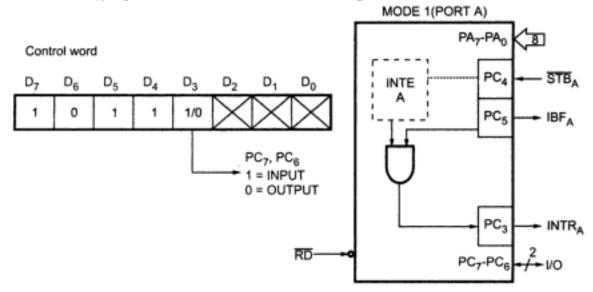

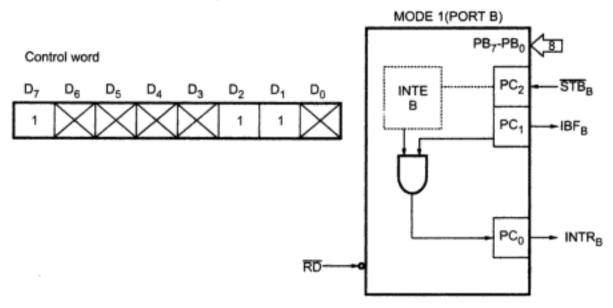

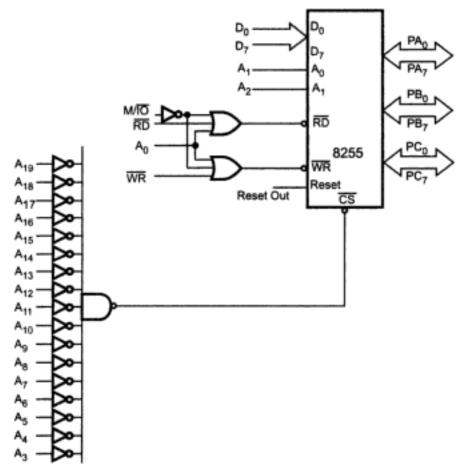

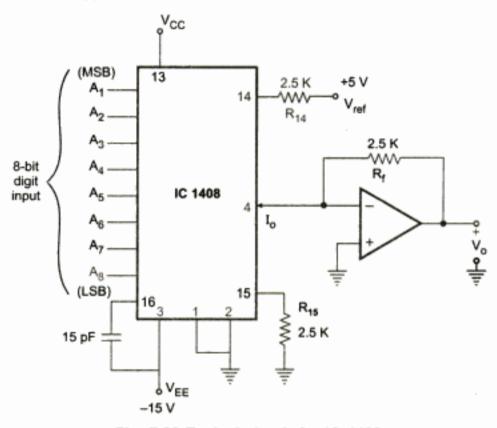

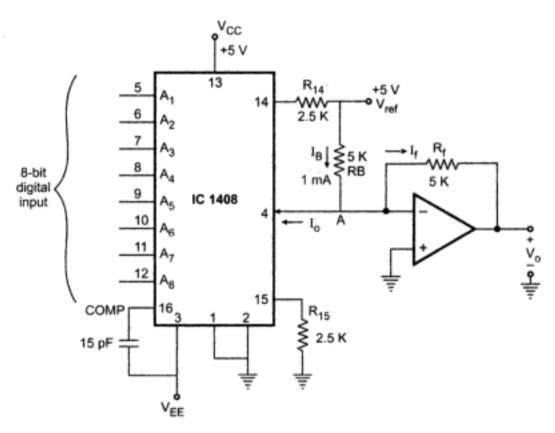

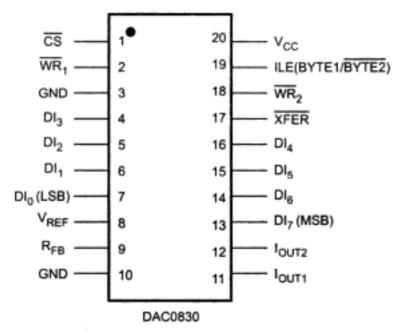

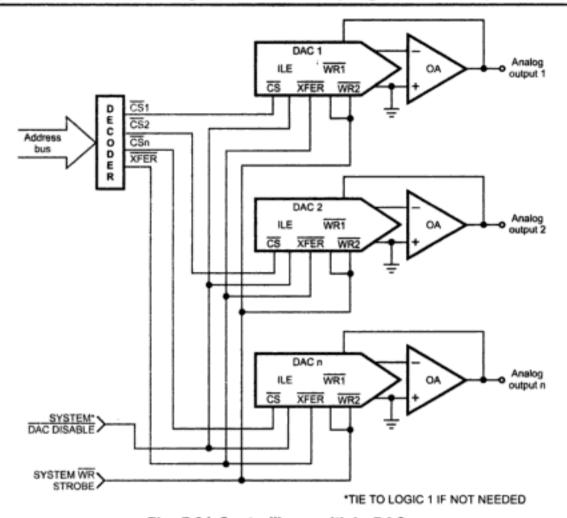

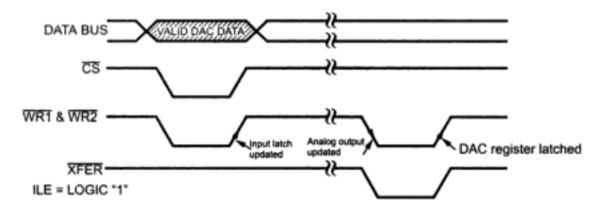

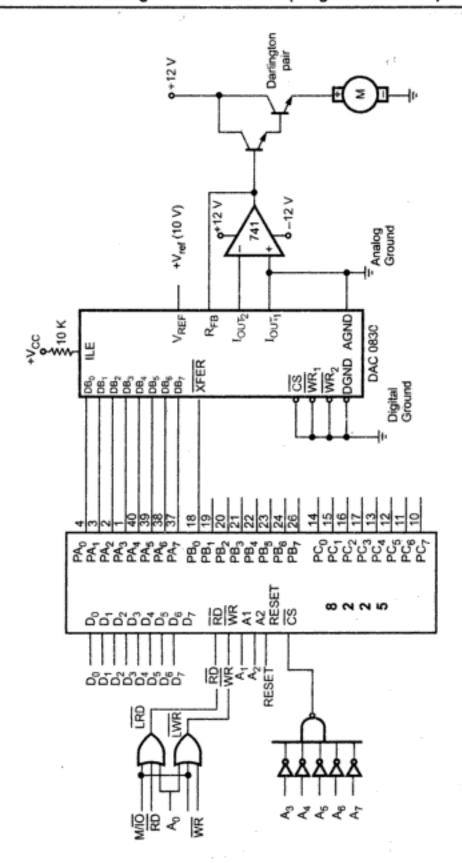

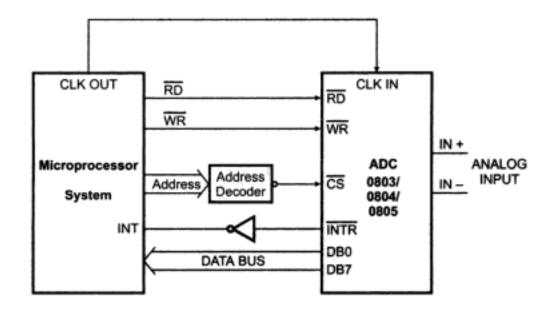

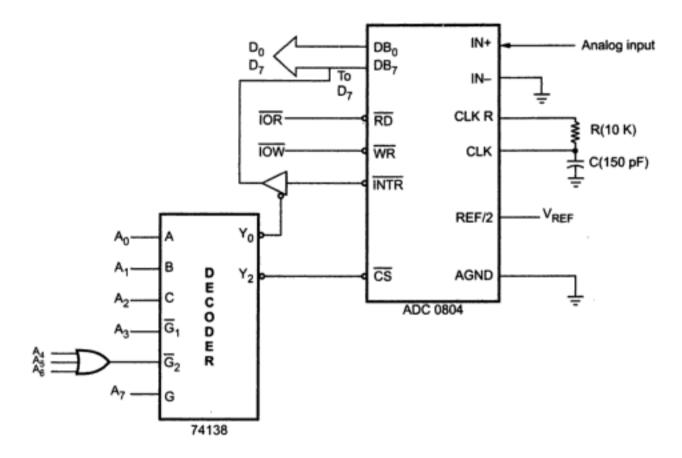

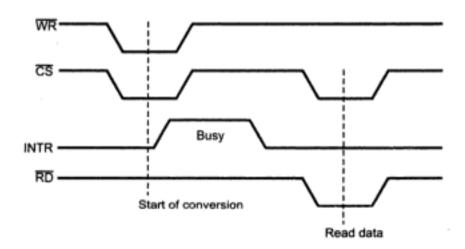

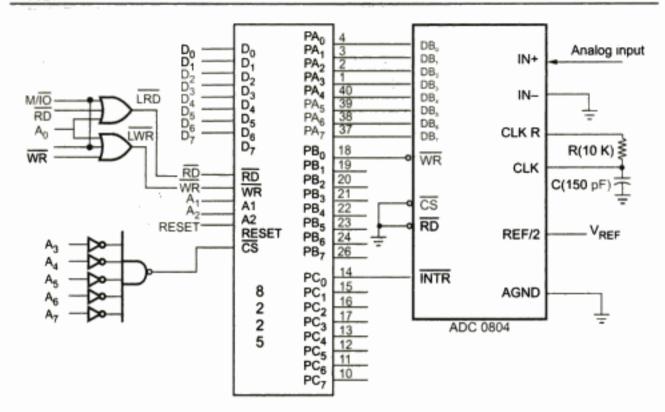

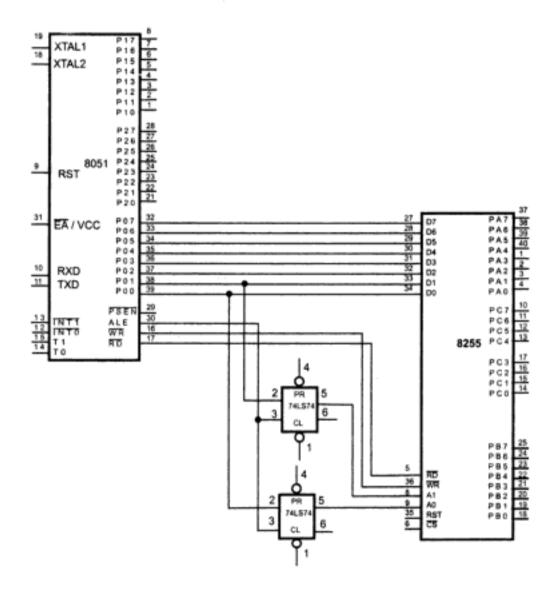

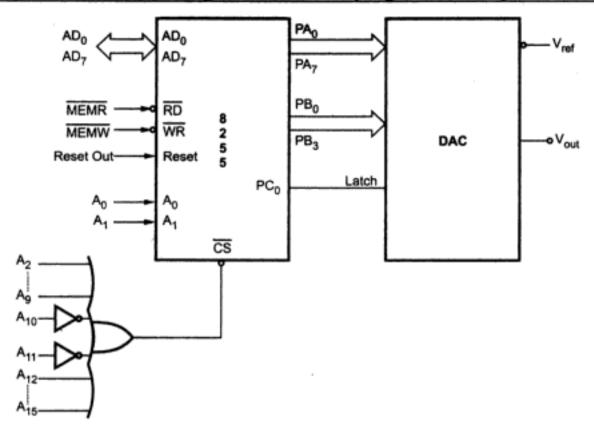

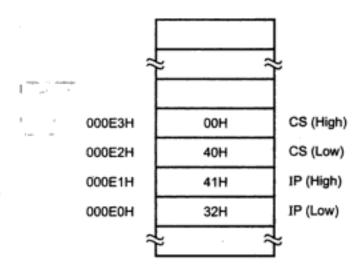

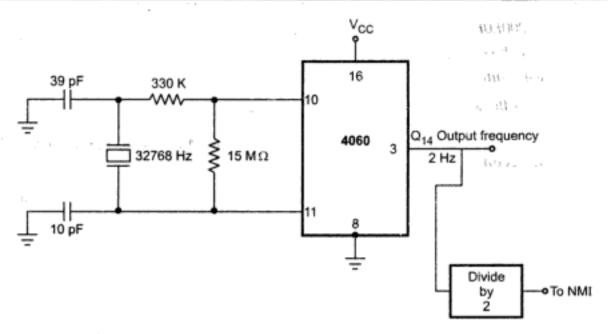

8255 PPI-Various modes of operation and interfacing to 8086, Interfacing keyboard, Displays, Stepper motor and actuators, D/A and A/D converter interfacing.

#### UNIT-VI (Chapter-8, 9)

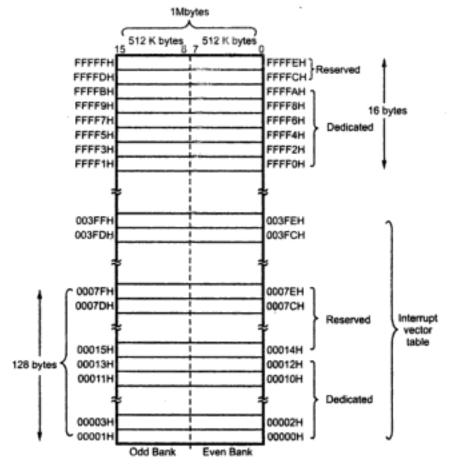

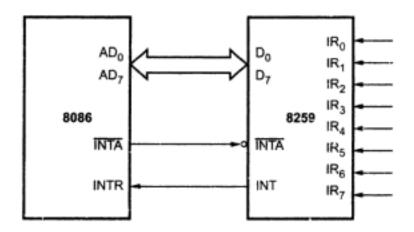

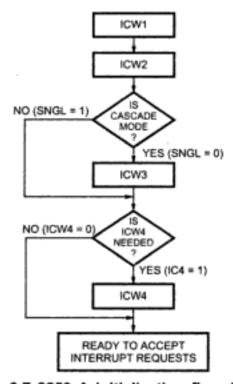

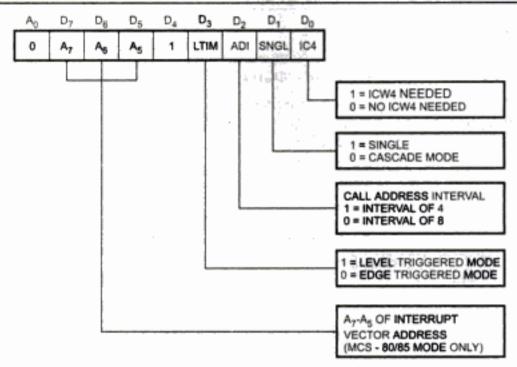

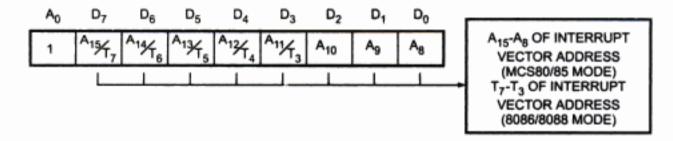

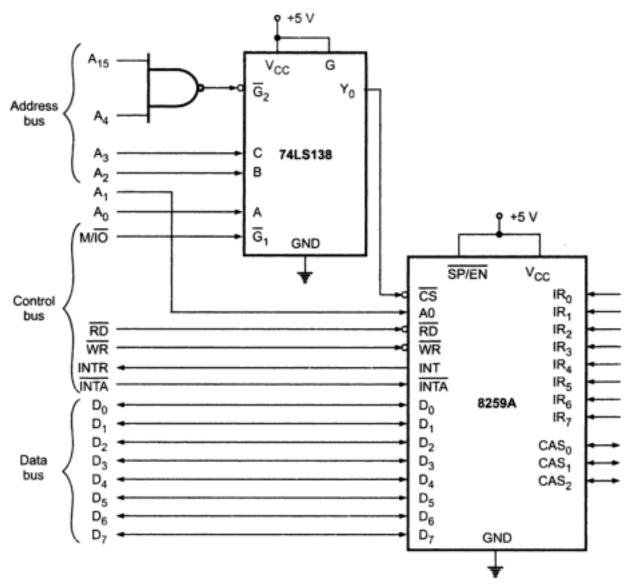

Interrupt structure of 8086, Vector interrupt table, Interrupt service routines, Introduction to DOS and BIOS interrupts, 8259 PIC architecture and interfacing cascading of interrupt controller and its importance.

#### UNIT-VII (Chapter-10)

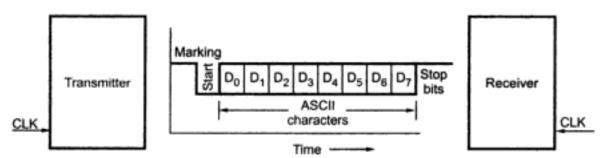

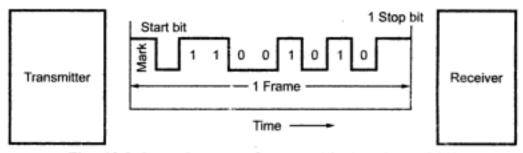

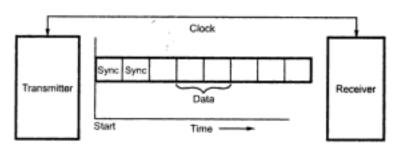

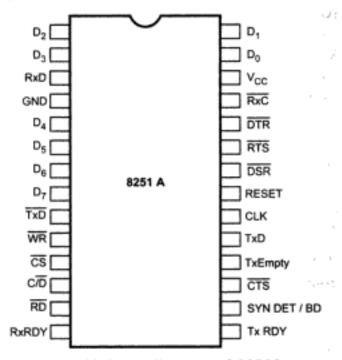

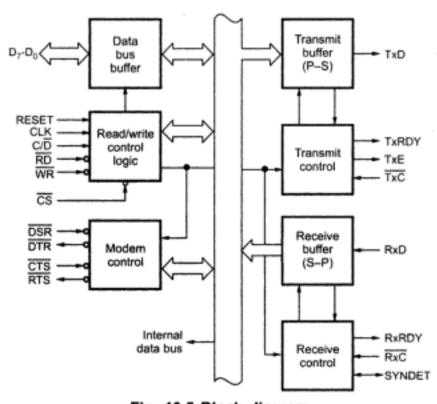

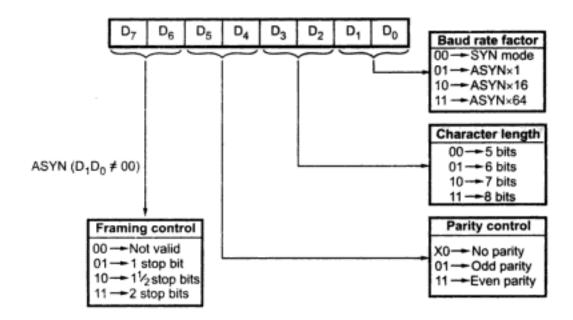

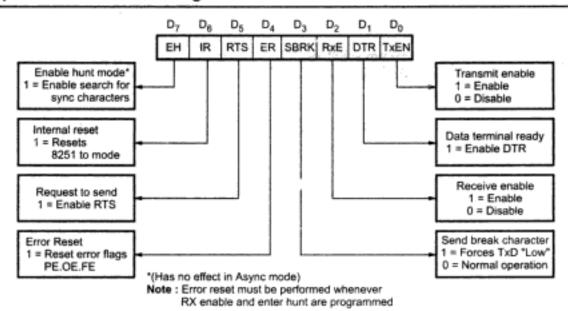

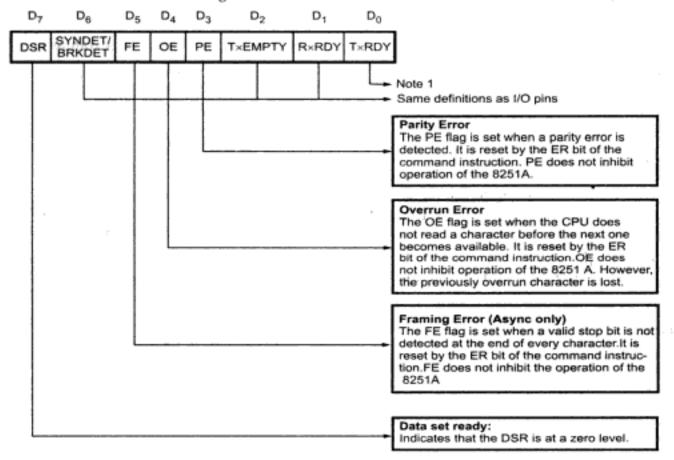

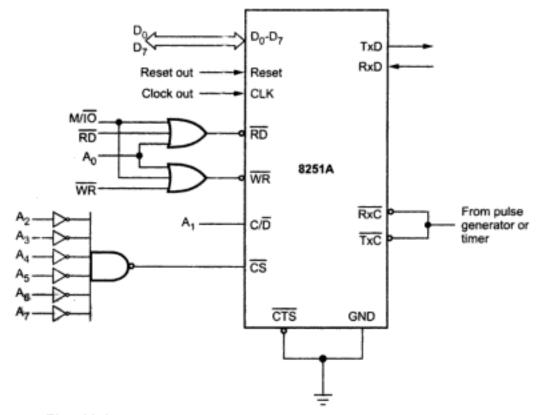

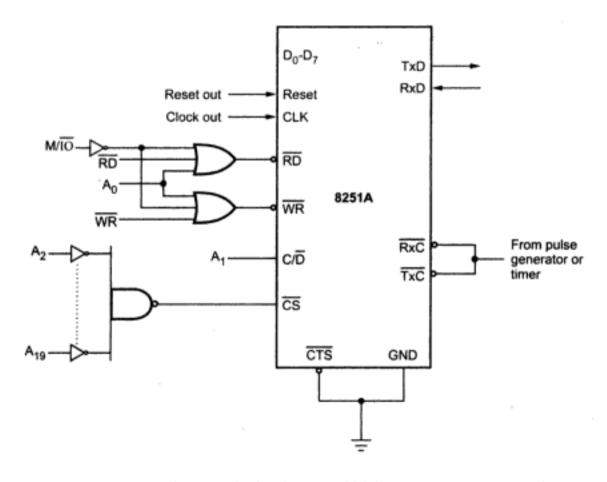

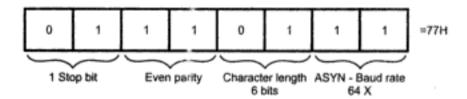

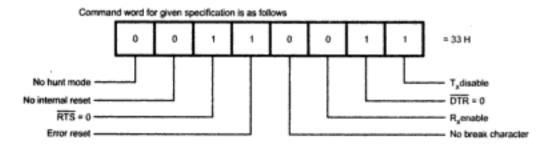

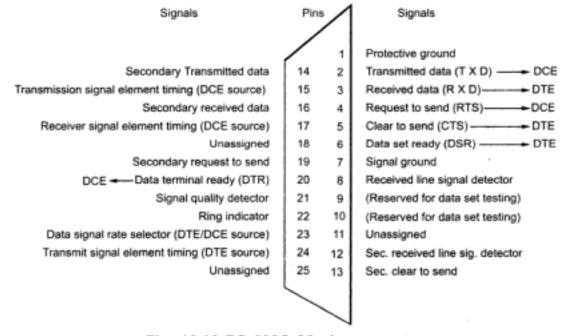

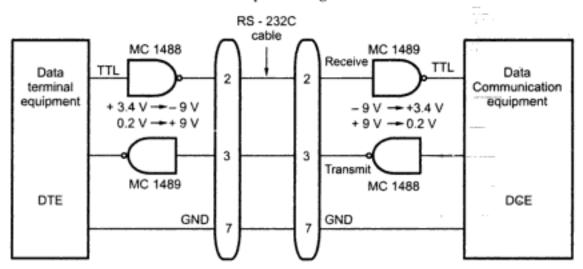

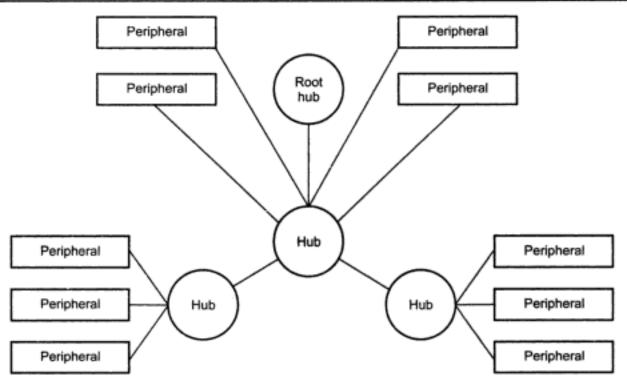

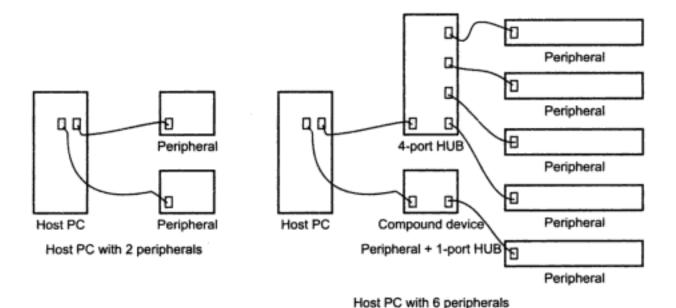

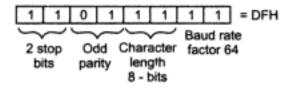

Serial data transfer schemes, Asynchronous and synchronous data transfer schemes, 8251 USART architecture and interfacing, TTL to RS 232C and RS232C to TTL conversion, Sample program of serial data transfer, Introduction to High-speed serial communications standards, USB.

#### UNIT-VIII (Chapter-11)

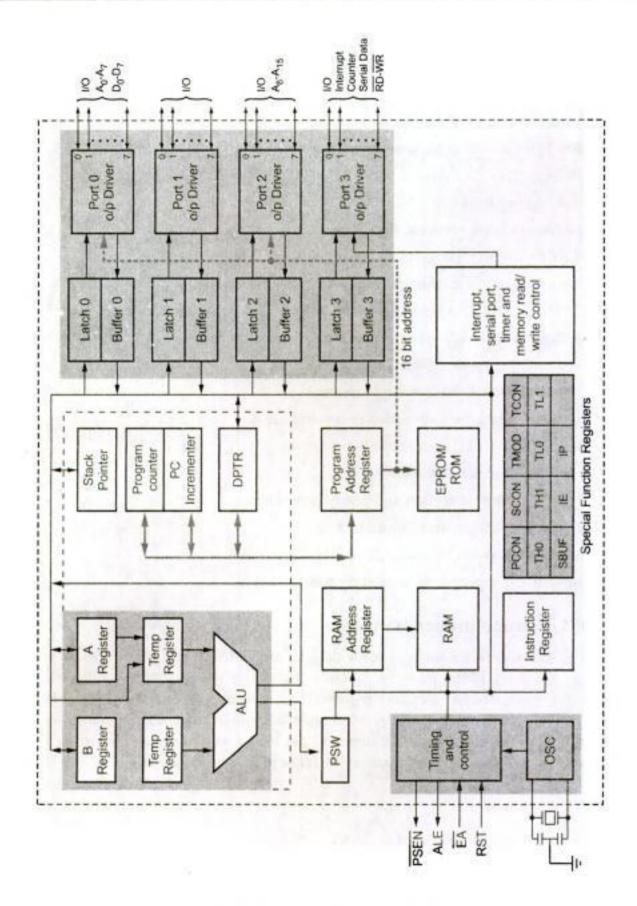

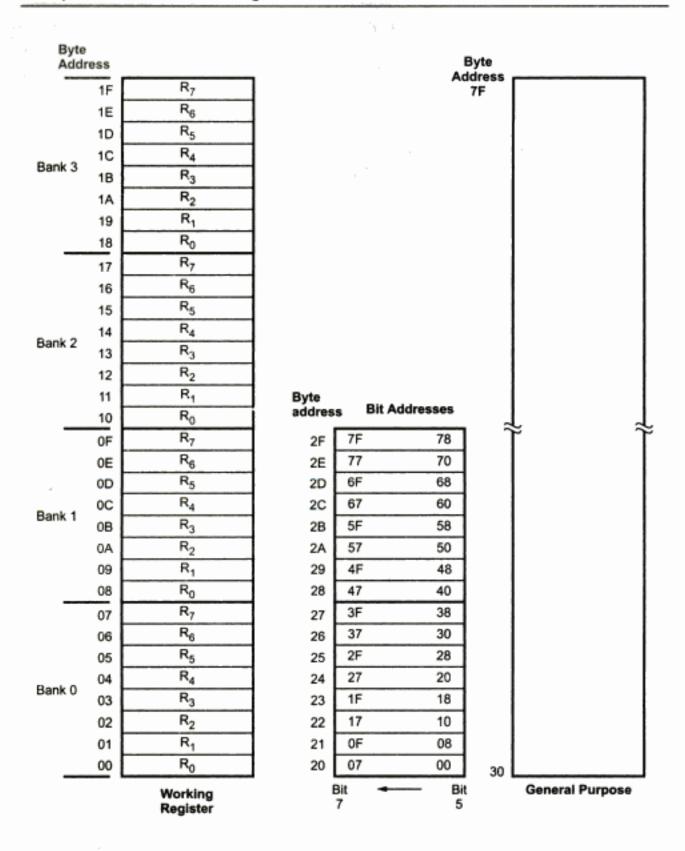

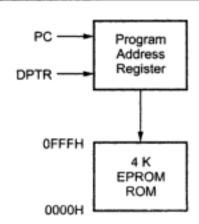

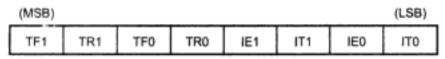

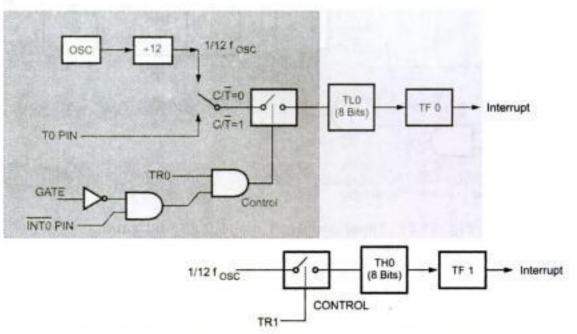

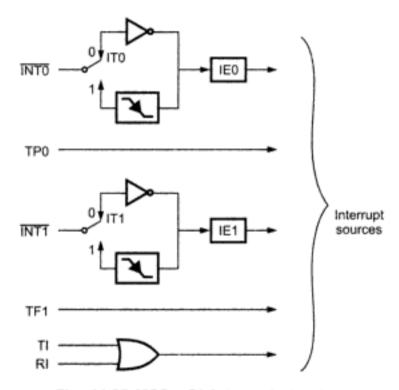

8051 Microcontroller architecture, Register set of 8051, Modes of timer operation, Serial port operation, Interrupt structure of 8051, Memory and I/O interfacing 8051.

| Table of Contents :                                               |                       |

|-------------------------------------------------------------------|-----------------------|

| Chapter 1 : An Overview of 8085                                   | (1 - 1) to (1 - 66)   |

| Chapter 2 : Architecture of 8086 Microprocessor                   | (2 - 1) to (2 - 14)   |

| Chapter 3: 8086 Instruction Set and Assembly Language Programming | (3 -1) to (3-110)     |

| Chapter 4 : Assembly Language Programs                            | (4 - 1) to (4 - 74)   |

| Chapter 5 : 8086 System Configuration                             | (5 - 1) to (5 -34)    |

| Chapter 6 : Direct Memory Access (DMA) - 8237/8257                | (6 - 1) to (6 - 28)   |

| Chapter 7 : 8255 PPI (Programmable Peripheral Interface)          | (7 - 1) to (7- 64)    |

| Chapter 8 : 8086 Interrupts                                       | (8 - 1) to (8 - 28)   |

| Chapter 9 : Introduction to DOS and BIOS Interrupts               | (9 - 1) to (9 - 30)   |

| Chapter 10 : Serial Communication                                 | (10 - 1) to (10 - 38) |

| Chapter 11 : 8051 Microcontroller                                 | (11 - 1) to (11 - 38) |

| Appendix - A                                                      | (A - 1) to (A - 6)    |

| Appendix - B                                                      | (B - 1) to (B - 10)   |

| Appendix - C                                                      | (C - 1) to (C - 8)    |

| Chapterwise University Questions with Answers                     | (P - 1) to (P - 34)   |

# Features of Book

- 8085, 8086/88 Architecture, programming and interfacing.

- Free download 8086 programs on www.vtubooks.com.

- 8051 Microcontroller architecture.

- Large number of programming examples.

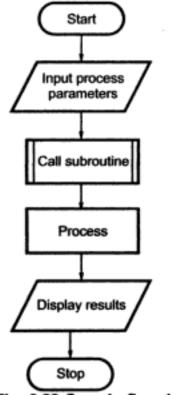

- Programs using modular programming approach.

- Practical interfacing design examples.

# Microprocessors & Interfacing

#### Atul P. Godse

M. S. Software Systems (BITS Pilani)

B.E. Industrial Electronics

Formerly Lecturer in Department of Electronics Engg.

Vishwakarma Institute of Technology

Pune

### Mrs. Deepali A. Godse

B.E. Industrial Electronics, M. E. (Computer)

Assistant Professor in Bharati Vidyapeeth's

Women's College of Engineering

Pune

Visit us at: www.vtubooks.com

Technical Publications Pune

## Microprocessors & Interfacing

ISBN 9788184311259

All rights reserved with Technical Publications. No part of this book should be reproduced in any form, Electronic, Mechanical, Photocopy or any information storage and retrieval system without prior permission in writing, from Technical Publications, Pune.

#### Published by:

Technical Publications Pune<sup>®</sup> #1, Amit Residency, 412, Shaniwar Peth, Pune - 411 030, India.

Printers: Vikram Printers 34, Parvati Industrial Estate Pune-Satara Road, Pune - 411009.

# **Preface**

Thanks to professors, students and authors of various technical books for their overwhelming response to our books. Looking at the feedback and the response we received from previous books, we are very pleased to release a text book on Microprocessors and its Applications.

The purpose of this book is to fulfil a need for text stating in plain, lucid and simple everyday language. This book provides a logical method for explaining and it prepares a background of the topic with essential illustrations. This text is provided with number of solved design examples which helps students to understand the application of microprocessor and microcontroller based systems.

The rapid spread of microprocessors in society has both simplified and complicated our lives. To get the conceptual view of the microprocessors, it is better to study them from the popular family like Intel. So we felt it is necessary to introduce a book which covers microprocessors and microcontroller with their features, internal architecture, internal organization and design details.

This text begins with the architecture of 8085 microprocessor. It explains all the details of 8085 microprocessor such as its architecture, pin description instruction set, memory and I/O interfacing and interrupts. The text then introduces a 16-bit microprocessor 8086. It also explains the details of 8086 like 8085. The text also explains various peripherals and their interfacing with microprocessors.

Finally, the text explains the 8051 microcontroller.

# Acknowledgement

We wish to express our profound thanks to all those who helped in making this book a reality. Much needed moral support and encouragement is provided on numerous occasions by our whole family.

We are specially grateful to the great teacher **Prof. A.V. Bakshi** for his time to time, much needed, valuable guidance. Without the full support and cheerful encouragement of **Mr. Uday Bakshi** the book would not have been completed in time.

Finally, we wish to thank Mr. Avinash Wani, Mr. Ravindra Wani and the entire team of Technical Publications who have taken immense pain to get the quality printing in time.

Any suggestions for the improvement of the book will be acknowledged and appreciated.

**Authors**

Atul Godse

Deepali Godse

Dedicated to Neha & Ruturaj

# **Table of Contents**

| Chapter 1 : An Overview of 8085                        | (1 - 1) to (1 - 66) |

|--------------------------------------------------------|---------------------|

| 1.1 8085 Microprocessor                                | 1 - 1               |

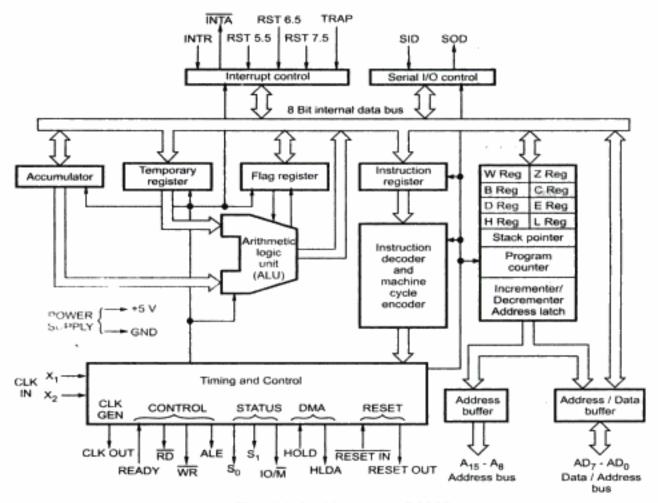

| 1.2 Architecture of 8085                               | 1 - 2               |

| 1.2.1 Register Structure                               | 1 - 3               |

| 1.2.2 Arithmetic Logic Unit (ALU)                      | 1 - 6               |

| 1.2.3 Instruction Decoder                              | 1-6                 |

| 1.2.4 Address Buffer                                   | 1-6                 |

| 1.2.5 Address/Data Buffer                              | 1-7                 |

| 1.2.6 Incrementer/Decrementer Address Latch            | 1-7                 |

| 1.2.7 Interrupt Control                                | 1 - 7               |

| 1.2.8 Serial I/O Control                               | 1-7                 |

| 1.2.9 Timing and Control Circuitry                     | 1 - 7               |

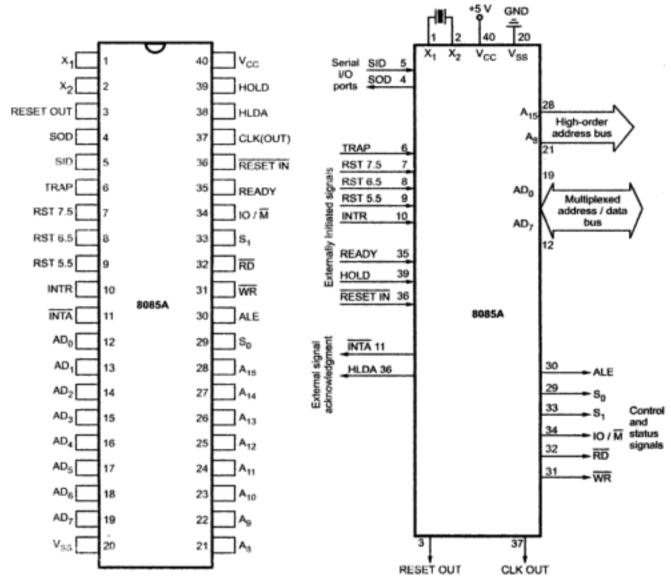

| 1.3 Pin Definitions of 8085                            | 1 - 8               |

| 1.3.1 Power Supply and Frequency Signals               | 1 - 9               |

| 1.3.2 Data Bus and Address Bus                         | 1-9                 |

| 1.3.3 Control and Status Signals                       | 1 - 9               |

| 1.3.4 Interrupt Signals                                | 1 - 10              |

| 1.3.5 Serial I/O Signals                               | 1 - 10              |

| 1.3.6 DMA Signal                                       | 1 - 10              |

| 1.3.7 Reset Signals                                    | 1 - 10              |

| 1.4 Bus Organisation                                   | 1 - 10              |

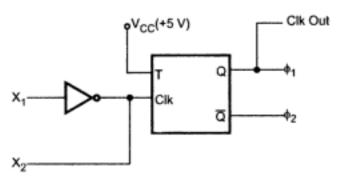

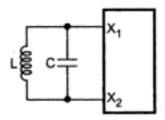

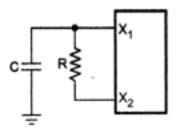

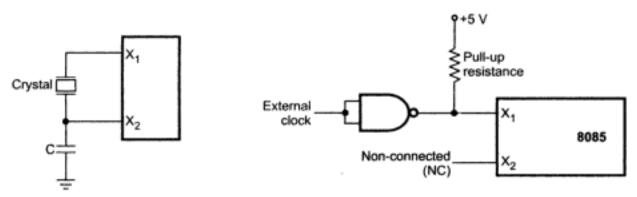

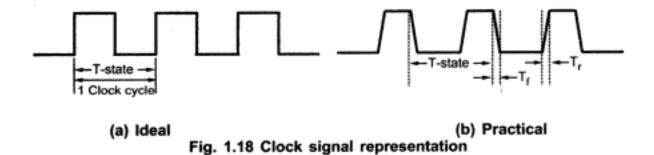

| 1.4.1 Clock Circuits.                                  | 1-11                |

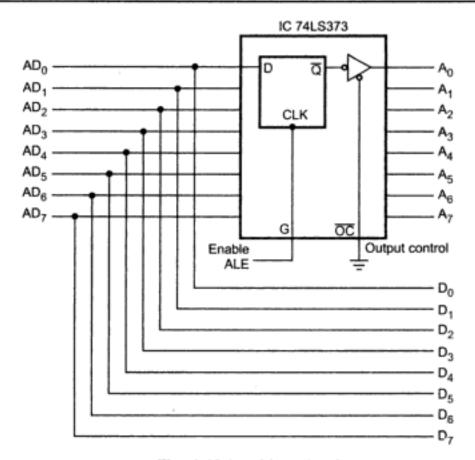

| 1.4.2 Demultiplexing AD <sub>2</sub> - AD <sub>0</sub> | 1 - 12              |

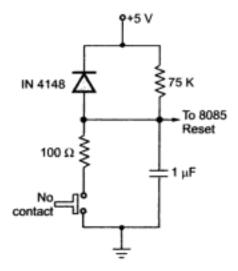

| 1.4.3 Reset Circuit                                    | 1 - 12              |

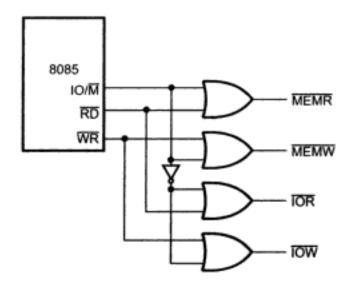

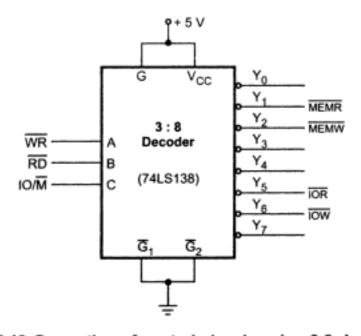

| 1.4.4 Generation of Control Signals                    | 1 - 14              |

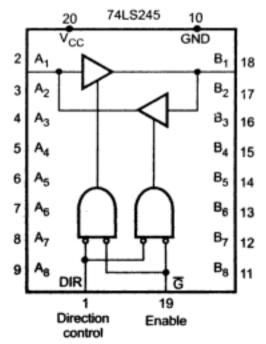

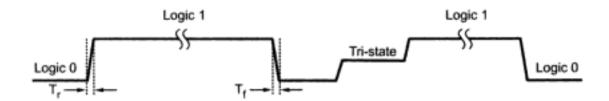

| 1.4.5 Bus Drivers                                      | 1 - 15              |

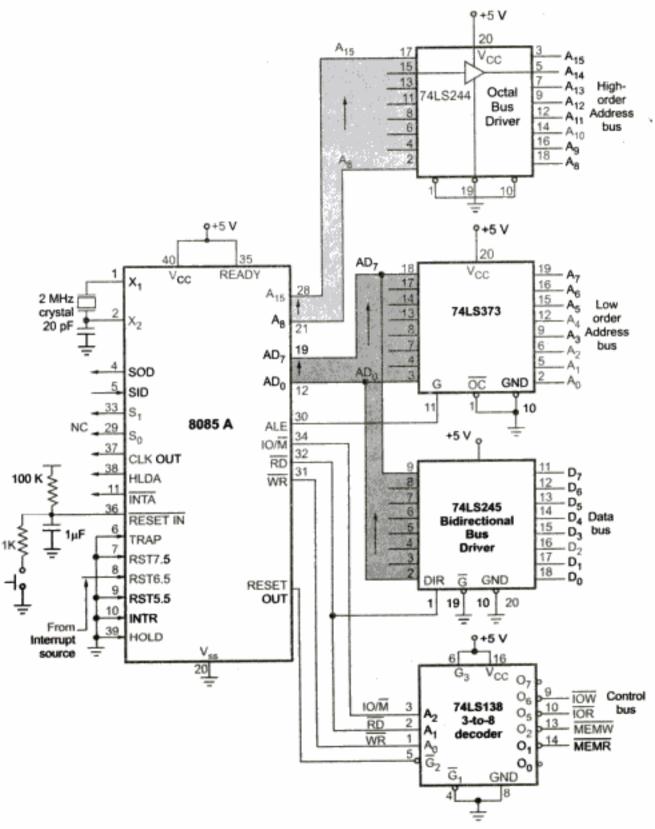

| 1.4.6 Typical Configuration                            | 1 - 17              |

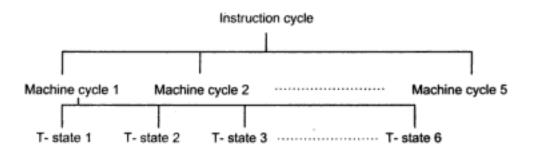

|    | 1.5 Timing and Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 - 18 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

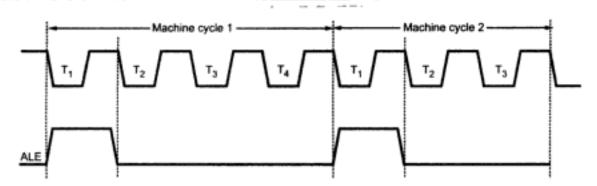

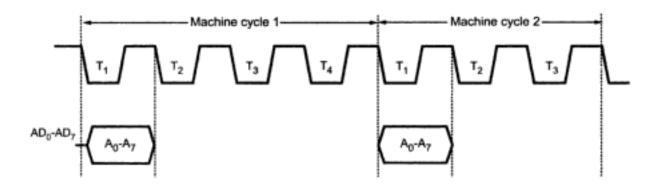

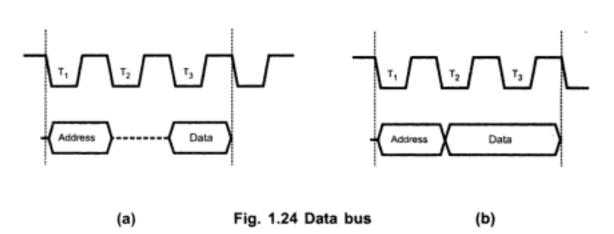

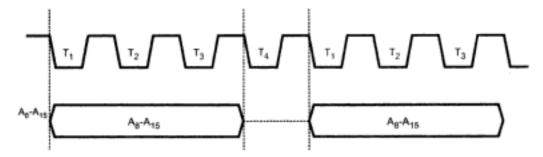

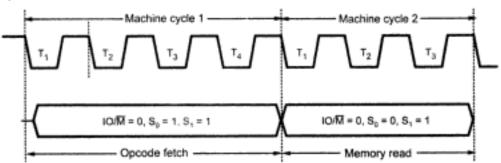

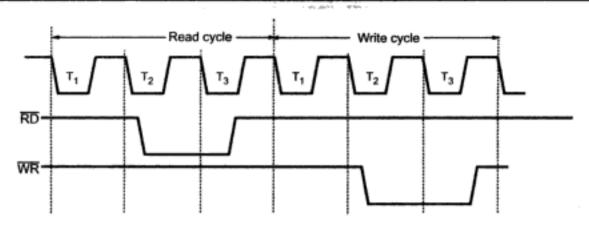

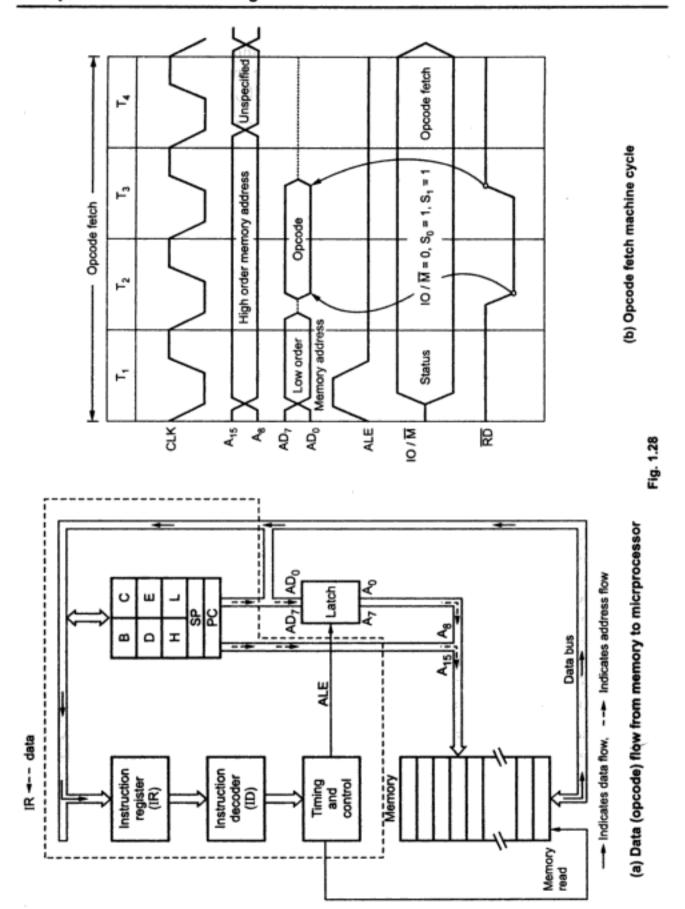

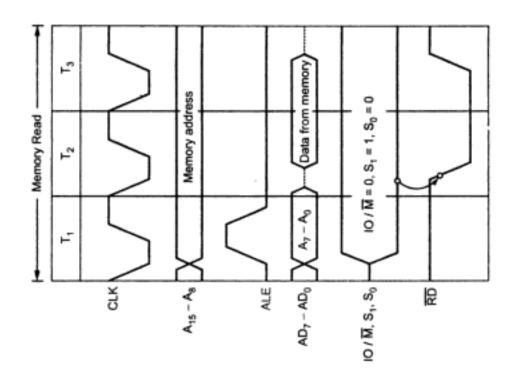

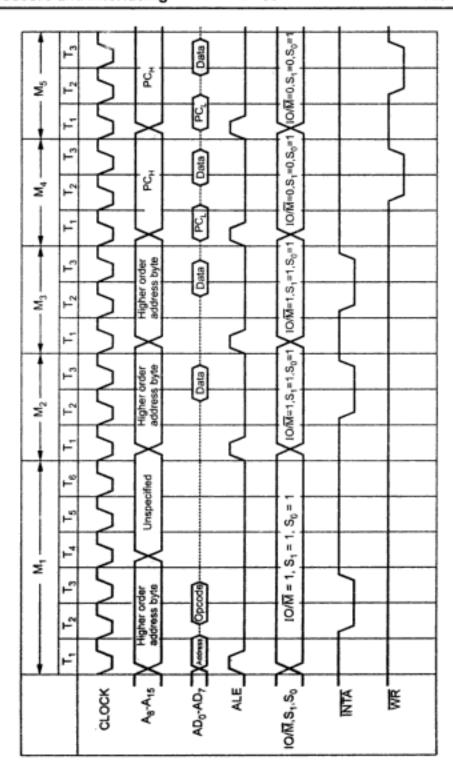

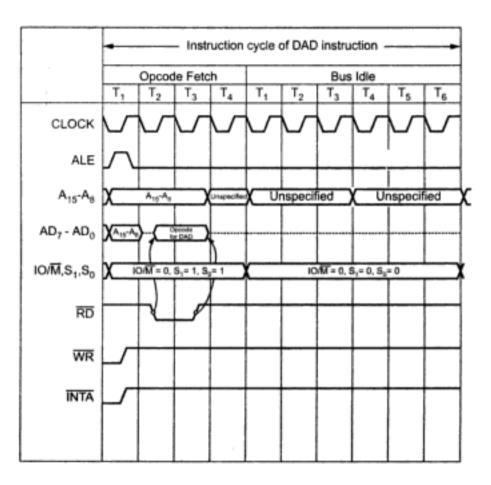

|    | 1.5.1 8085 Machine Cycles and their Timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 - 24 |

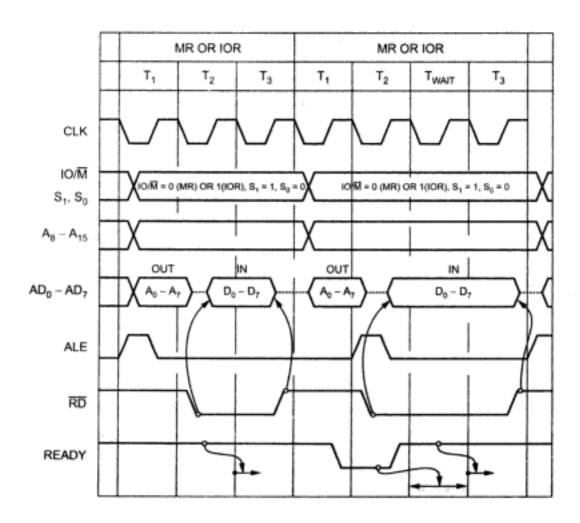

|    | 1.5.2 Concept of Wait States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 - 35 |

|    | 1.6 Instruction Set of 8085                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 - 37 |

|    | 1.6.1 Data Transfer Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 - 37 |

|    | 1.6.2 Arithmetic Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 - 39 |

|    | 1.6.3 Branch Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 - 45 |

|    | 1.6.4 Logic Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 - 48 |

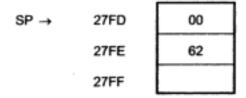

|    | 1.6.5 Stack Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 - 52 |

|    | 1.6.6 Machine Control Group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 - 54 |

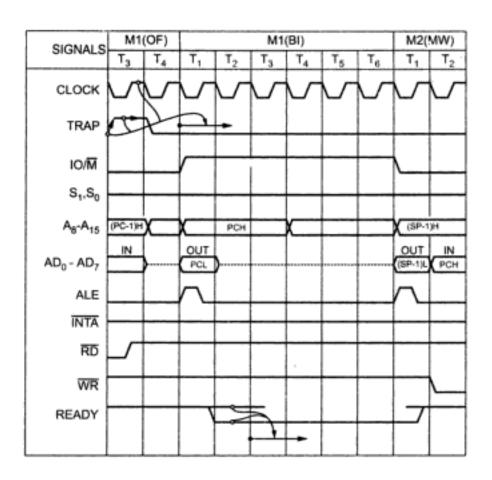

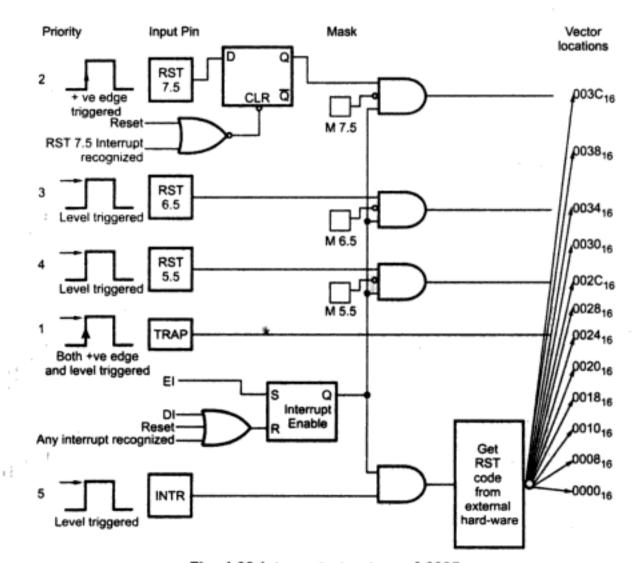

|    | 1.7 8085 Interrupt Structure and Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 - 55 |

|    | 1.7.1 Types of Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1 - 55 |

|    | 1.7.2 Overall Interrupt Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-56   |

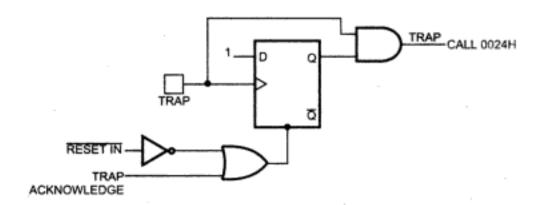

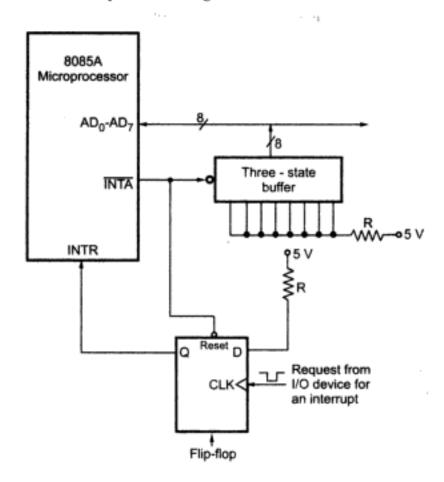

|    | 1.7.2.1 Hardware Interrupts in 8085                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-56   |

|    | 1.7.2.2 Software Interrupts in 8085                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-60   |

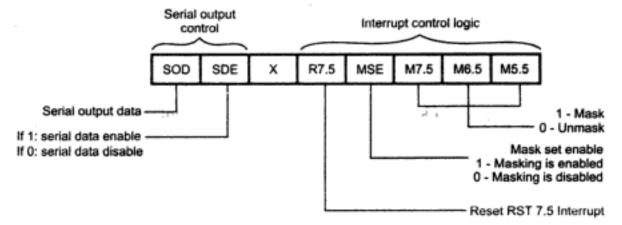

|    | 1.7.3 Masking / Unmasking of Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-60   |

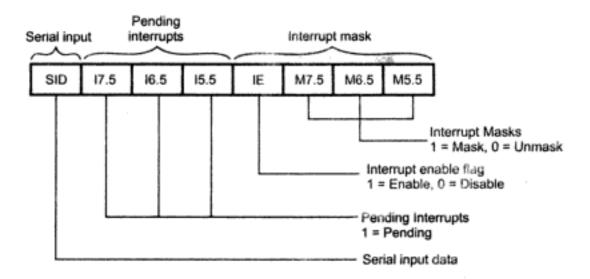

|    | 1.7.4 Pending Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 - 62 |

|    | Review Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 - 65 |

| Ch | napter 2 : Architecture of 8086 Microprocessor (2 - 1) to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (2-14) |

|    | 2.1 Features of 8086                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2 - 1  |

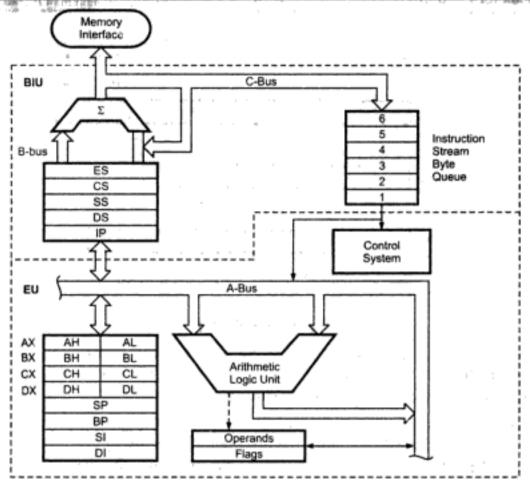

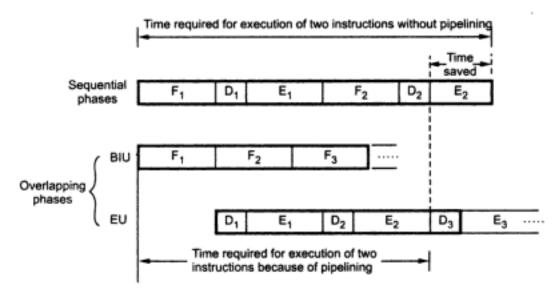

|    | 2.2 Architecture of 8086                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2 - 2  |

|    | 2.2.1 Bus Interface Unit [BIU]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |

|    | 2.2.2 Execution Unit [EU]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

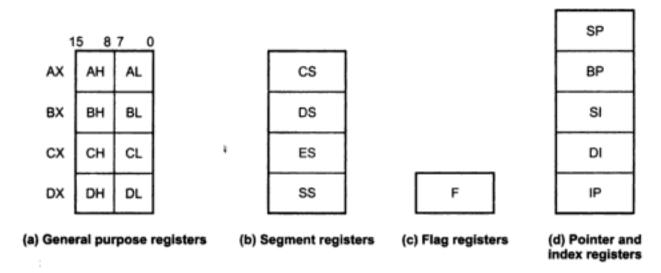

|    | 2.3 Register Organisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |

|    | 2.3.1 General Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |

|    | 2.3.2 Segment Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

|    | 2.3.3 Pointers and Index Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

|    | 2.3.4 Flag Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

|    | 2.4 Bus Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

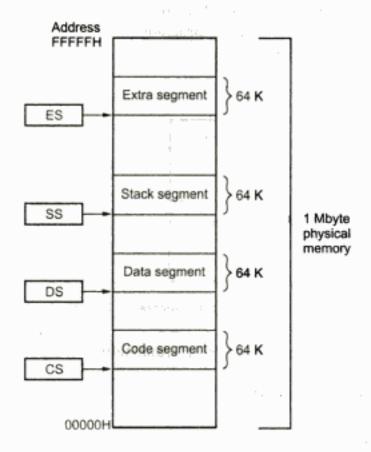

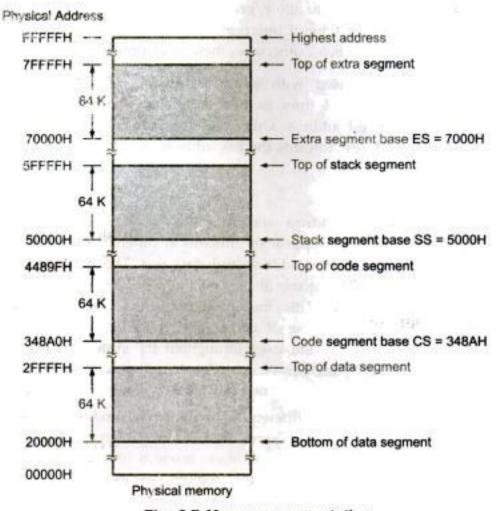

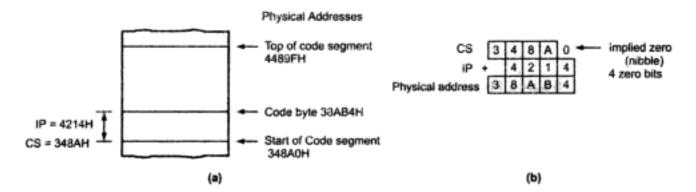

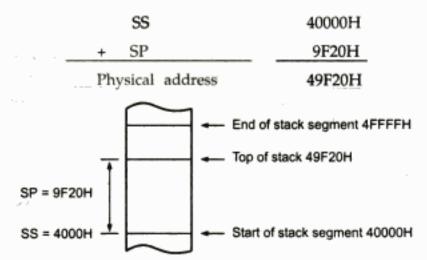

|    | 2.5 Memory Segmentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

|    | Review Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

|    | TO A LOCAL OF THE PARTY OF THE | 14     |

| apter 3: 8086 Instruction Set and Assembly Language Programming | (3 -1) to (3-110). |

|-----------------------------------------------------------------|--------------------|

| 3.1 Introduction                                                | 3 - 1              |

| 3.2 Addressing Modes                                            | 3 - 1              |

| 3.2.1 Data Addressing Modes                                     | 3 - 1              |

| 3.2.2 Program Memory Addressing Modes                           | 3-9                |

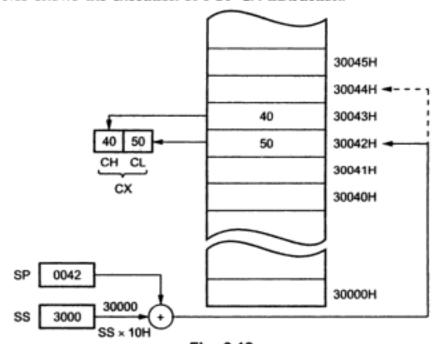

| 3.2.3 Stack Memory Addressing Modes                             | 3 - 11             |

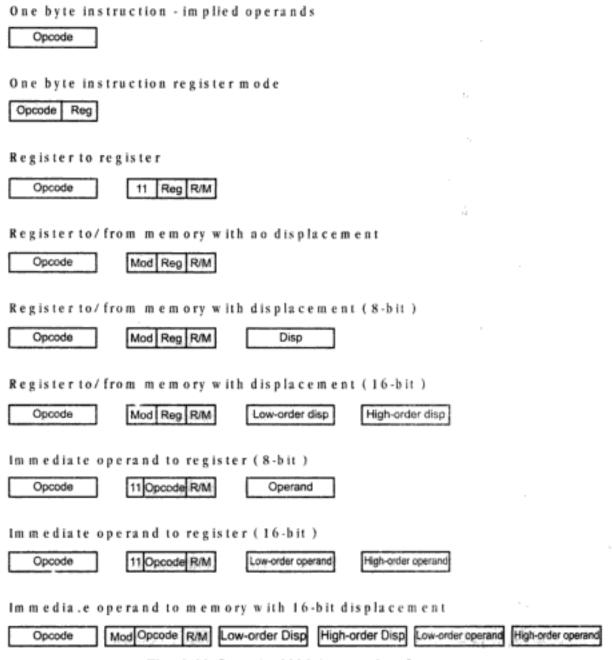

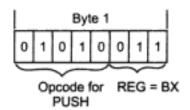

| 3.3 Instruction Set of 8086/8088                                | 3 - 14             |

| 3.4 Data Movement Instructions                                  | 3 - 15             |

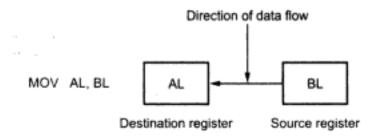

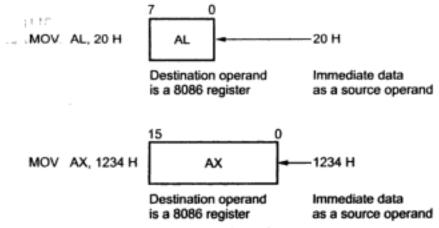

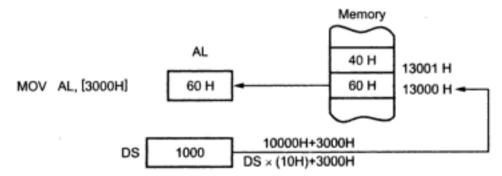

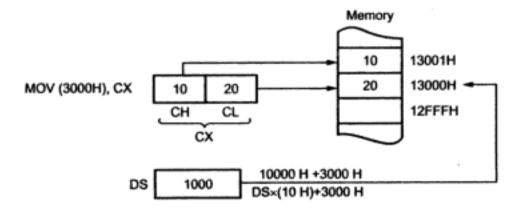

| 3.4.1 MOV Instruction                                           | 3 - 15             |

| 3.4.2 PUSH/POP Instructions.                                    | 3 - 16             |

| 3.4.3 Load Effective Address                                    | 3 - 18             |

| 3.4.4 String Data Transfer Instructions                         | 3 - 19             |

| 3.4.5 Miscellaneous Data Transfer Instructions                  | 3 - 21             |

| 3.5 Arithmetic and Logic Instructions                           | 3 - 23             |

| 3.5.1 Addition                                                  | 3 - 23             |

| 3.5.2 Subtraction                                               | 3 - 25             |

| 3.5.3 Comparison                                                | 3 - 26             |

| 3.5.4 Multiplication                                            | 3 - 27             |

| 3.5.5 Division                                                  | 3 - 28             |

| 3.5.6 BCD and ASCII Arithmetic                                  | 3 - 28             |

| 3.5.6.1 BCD Arithmetic                                          | 3-29               |

| 3.5.6.2 ASCII Arithmetic                                        | 3 - 30             |

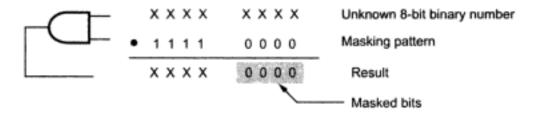

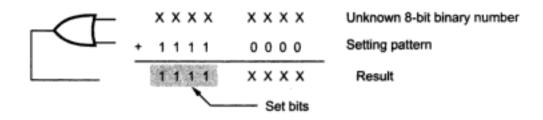

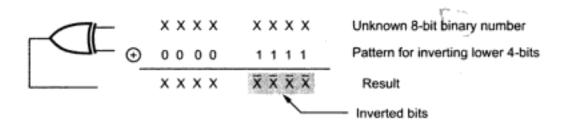

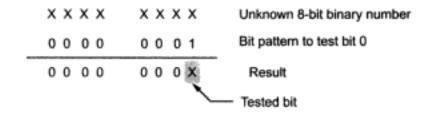

| 3.5.7 Basic Logic Instructions                                  | 3 - 32             |

| 3.5.8 Shift and Rotate                                          | 3 - 36             |

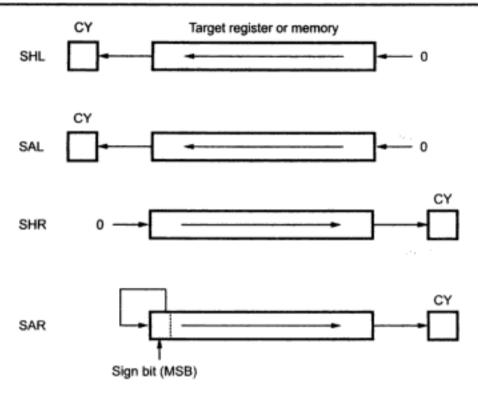

| 3.5.8.1 Shift                                                   | 3-36               |

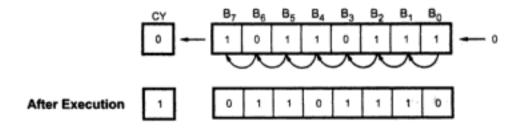

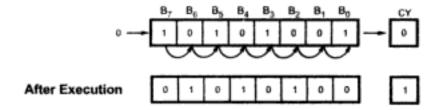

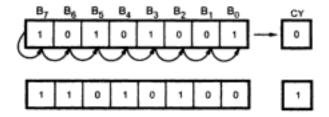

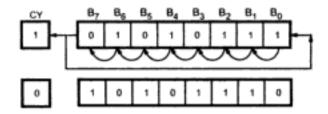

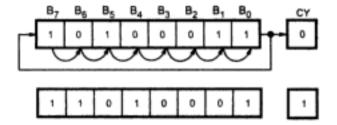

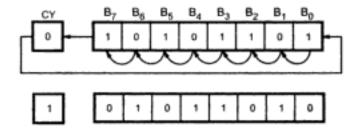

| 3.5.8.2 Rotate                                                  | 3-39               |

| 3.6 String Instructions                                         | 3 - 42             |

| 3.7 Program Control Transfer Instructions                       | 3 - 44             |

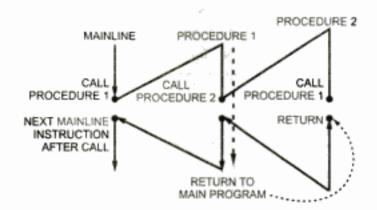

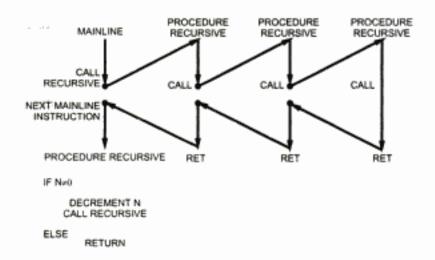

| 3.7.1 CALL and RET Instructions                                 | 3 - 44             |

| 3.7.2 JMP Instruction                                           | 3 - 46             |

| 3.7.3 Cond - Conditional Jump                                   | 3 - 48             |